Source: Hack a Day

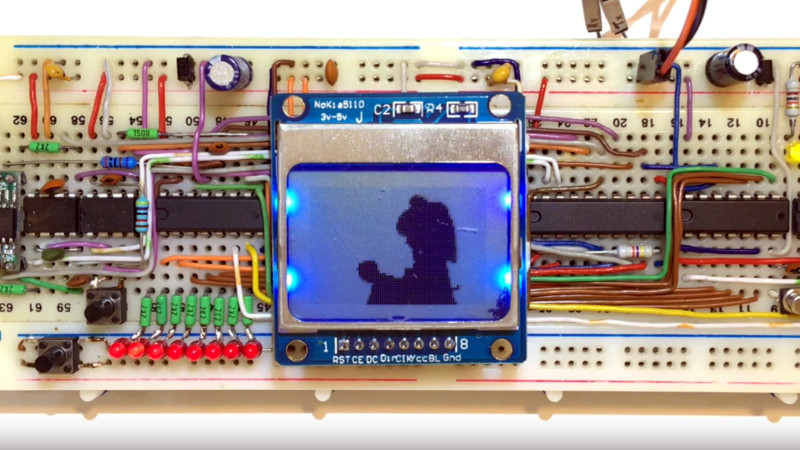

We’re no stranger to homemade CPUs on these pages, but we think that [Jiri Stepanovsky]’s 16-bit serial CPU might be a little special. Why? It has an astonishingly low chip count, with only 8 ICs in total. How on earth does he do it?

While a traditional TTL CPU has a relatively high chip count due to a parallel data bus, registers, and discrete ALU, this one takes a few shortcuts by opting for a one-bit serial bus with serial memory chips and an EPROM serving as a look-up-table ALU. Perhaps the most interesting result of this architecture is that it also allows the CPU to dispense with registers, like the Texas Instruments 16-bit chips back in the day. They all live in memory. You can see it below the break in action, streaming a video to a Nokia-style LCD.

Such a CPU would indeed have been unlikely to have been made back in the day due to the prohibitive cost of buying and programming such a large EPROM. However, old computers like the EDSAC also used a serial data path and mercury delay line memory to manage complexity. But for a solid-state CPU in 2023, we think the design is innovative. We think it would be challenging to reduce the chip count further — and no, we’re not counting designs that use a microcontroller to replicate a block of circuitry; that’s cheating — but we’re sure that somewhere there’s a designer with ideas for slimming the design further.

Thanks to [Ken Boak] for the tip.